# Datasheet for BLE SoC ST17H56

DS-ST17H56-E1

Ver 0.8.0

# 2020/11/24

# **Keyword:**

BLE; 2.4GHz; Features; Package; Pin layout; Memory; MCU; Working modes; Wakeup sources; RF Transceiver; Baseband; Clock; Timers; Interrupt; Interface; PWM; QDEC; ADC; PGA; AES; Electrical specification

# **Brief:**

This datasheet is dedicated for BLE SoC ST17H56. In this datasheet, key features, working mode, main modules, electrical specification and application of the ST17H56 are introduced.

# **Revision History**

| Version | Major Changes       | Date    | Author       |

|---------|---------------------|---------|--------------|

| 0.8.0   | Preliminary release | 2020/11 | CLX, YLJ, YH |

# 1 Table of contents

| 1 | Ove  | ervie | w                                                | . 6 |

|---|------|-------|--------------------------------------------------|-----|

|   | 1.1  | Bloc  | ck diagram                                       | . 6 |

|   | 1.2  | Key   | features                                         | . 7 |

|   | 1.2. | 1     | General features                                 | . 7 |

|   | 1.2. | 2     | RF Features                                      | . 8 |

|   | 1.2. | .3    | Features of power management module              | . 8 |

|   | 1.3  | Тур   | ical application                                 | . 9 |

|   | 1.4  | Ord   | ering information                                | . 9 |

|   | 1.5  | Pac   | kage                                             | . 9 |

|   | 1.6  | Pin   | layout                                           | 11  |

|   | 1.6. | 1     | Pin layout for ST17H56                           | 11  |

|   | 1.6. | 2     | Notes                                            | 12  |

| 2 | Me   | mory  | y and MCU                                        | 13  |

|   | 2.1  | Me    | emory                                            | 13  |

|   | 2.1. | 1     | SRAM/Register                                    | 13  |

|   | 2.1. | 2     | OTP                                              | 13  |

|   | 2.2  | Fir   | mware encryption                                 | 14  |

|   | 2.3  | M     | CU                                               | 14  |

|   | 2.4  | W     | orking modes                                     | 14  |

|   | 2.4. | 1     | Active mode                                      | 14  |

|   | 2.4. | 2     | Idle mode                                        | 15  |

|   | 2.4. | .3    | Power-saving mode                                | 15  |

|   | 2.5  | Res   | et                                               | 17  |

|   | 2.6  | Pow   | ver Management                                   | 18  |

|   | 2.6. | 1     | Digital LDO                                      | 18  |

|   | 2.6. | 2     | VBUS LDO                                         | 18  |

|   | 2.6. | .3    | Power-On-Reset (POR) and Brown-out detect        | 18  |

|   | 2.6. | 4     | Working mode switch                              | 21  |

|   | 2.7  | Wal   | keup sources                                     | 22  |

|   | 2.7. | 1     | Wakeup source – 32kHz timer                      | 22  |

|   | 2.7. | 2     | Wakeup source – IO                               | 22  |

|   | 2.7. | .3    | Register table                                   | 22  |

| 3 | BLE  | /2.4  | G RF Transceiver                                 | 24  |

|   | 3.1  | Bloc  | ck diagram                                       | 24  |

|   | 3.2  | Fun   | ction description                                | 24  |

|   | 3.2. | 1     | Air interface data rate and RF channel frequency | 24  |

|   | 3.3  | Base  | eband                                            | 24  |

|   | 3.3. | 1     | Packet format                                    | 25  |

|   | 3.3. | 3     | RSSI and frequency offset                        | 25  |

| 4 | Clock    |                                                          | 26 |

|---|----------|----------------------------------------------------------|----|

|   | 4.1 Clo  | ock sources                                              | 26 |

|   | 4.2 Sy   | stem clock                                               | 27 |

|   | 4.3 M    | odule clock                                              | 27 |

|   | 4.3.1    | System Timer clock                                       | 27 |

|   | 4.3.2    | QDEC clock                                               | 27 |

|   | 4.4 Re   | gister table                                             | 28 |

| 5 | Timers.  |                                                          | 29 |

|   | 5.1 Tim  | er0~Timer2                                               | 29 |

|   | 5.1.1    | Register table                                           | 29 |

|   | 5.1.2    | Mode0 (System Clock Mode)                                | 30 |

|   | 5.1.3    | Mode1 (GPIO Trigger Mode)                                | 30 |

|   | 5.1.4    | Mode2 (GPIO Pulse Width Mode)                            | 31 |

|   | 5.1.5    | Mode3 (Tick Mode)                                        | 32 |

|   | 5.1.6    | Watchdog                                                 | 32 |

|   | 5.2 32k  | Hz LTIMER                                                | 33 |

|   | 5.3 Syst | em Timer                                                 | 33 |

| 6 | Interrup | ot System                                                | 36 |

|   | 6.1 Inte | rrupt structure                                          | 36 |

|   | 6.2 Reg  | ister configuration                                      | 36 |

|   | 6.2.1    | Enable/Mask interrupt sources                            | 37 |

|   | 6.2.2    | Interrupt mode and priority                              | 37 |

|   | 6.2.3    | Interrupt source flag                                    | 38 |

| 7 | Interfac | e                                                        | 39 |

|   | 7.1 GPI  | 0                                                        | 39 |

|   | 7.1.1    | Basic configuration                                      | 39 |

|   | 7.1.1    | .1 GPIO lookup table                                     | 39 |

|   | 7.1.1    | .2 Multiplexed functions                                 | 41 |

|   | 7.1.1    | .3 Drive strength                                        | 41 |

|   | 7.1.2    | Connection relationship between GPIO and related modules | 41 |

|   | 7.1.3    | Pull-up/Pull-down resistor                               | 44 |

|   |          | 5                                                        |    |

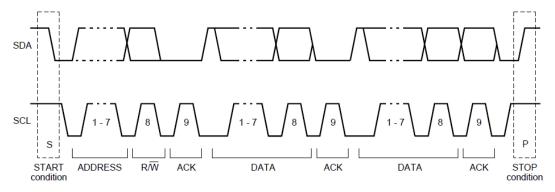

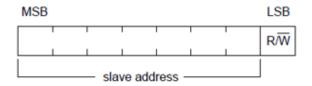

|   | 7.3 I2C  |                                                          | 46 |

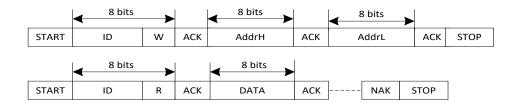

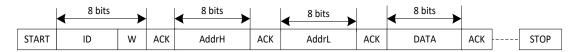

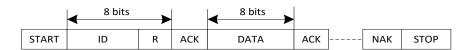

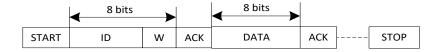

|   | 7.3.1    | Communication protocol                                   | 46 |

|   | 7.3.2    | Register table                                           | 46 |

|   | 7.3.3    | I2C Slave mode                                           | 47 |

|   | 7.3.3    | .1 DMA mode                                              | 48 |

|   | 7.3.3    | .2 Mapping mode                                          | 48 |

|   |          | I2C Master mode                                          |    |

|   | 7.3.4    | .1 I2C Master Write transfer                             | 49 |

|   | 7.3.4    | .2 I2C Master Read transfer                              | 50 |

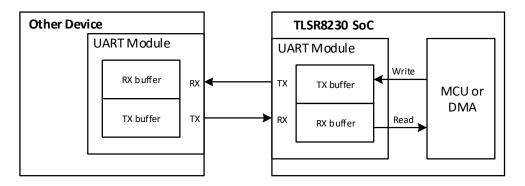

|   | 7.4 UAF  | RT                                                       | 50 |

| 8  | PW    | M                                              | 53 |

|----|-------|------------------------------------------------|----|

|    | 8.1   | Register table                                 | 53 |

|    | 8.2   | Enable PWM                                     | 55 |

|    | 8.3   | Set PWM clock                                  | 55 |

|    | 8.4   | PWM waveform, polarity and output inversion    | 55 |

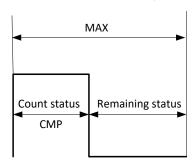

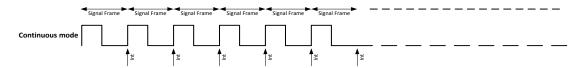

|    | 8.4.  | 1 Waveform of signal frame                     | 55 |

|    | 8.4.  | 2 Invert PWM output                            | 55 |

|    | 8.4.  | 3 Polarity for signal frame                    | 56 |

|    | 8.5   | PWM mode                                       | 56 |

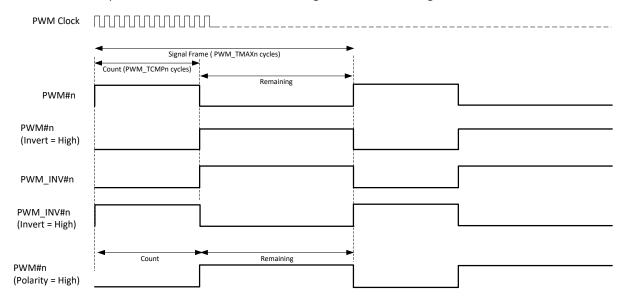

|    | 8.5.  | 1 Continuous mode                              | 56 |

|    | 8     | 3.5.1.1 Set PWM clock mode                     | 57 |

|    | 8.6   | PWM interrupt                                  | 57 |

| 9  | Qua   | adrature Decoder                               | 58 |

|    | 9.1   | Input pin selection                            | 58 |

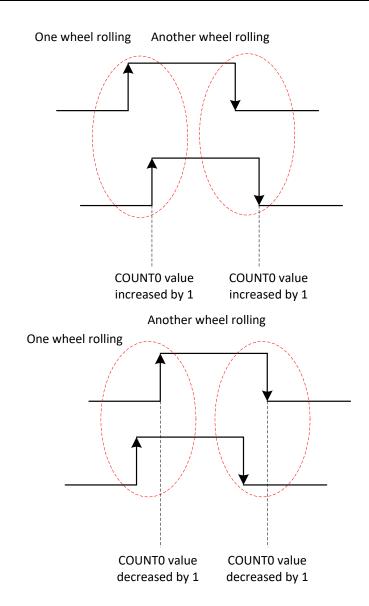

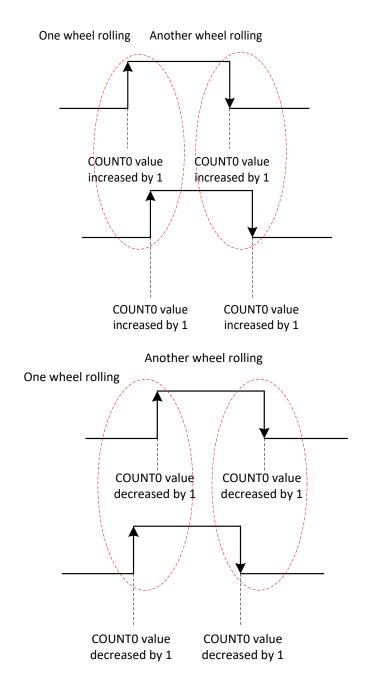

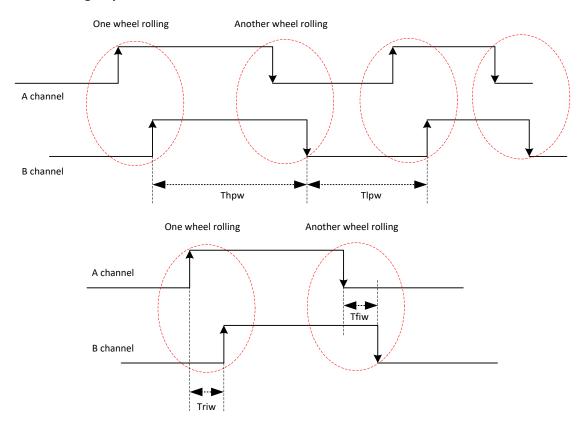

|    | 9.2   | Common mode and double accuracy mode           | 58 |

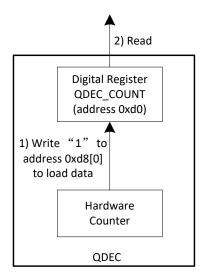

|    | 9.3   | Read real time counting value                  | 60 |

|    | 9.4   | QDEC reset                                     | 61 |

|    | 9.5   | Other configuration                            | 61 |

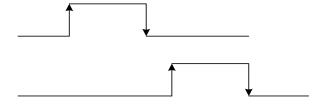

|    | 9.6   | Timing sequence                                | 62 |

|    | 9.7   | Register table                                 | 63 |

| 10 | ) SAR | ADC                                            | 64 |

|    | 10.1  | Power on/down                                  |    |

|    | 10.2  | ADC clock                                      | 64 |

|    | 10.3  | ADC control in auto mode                       | 64 |

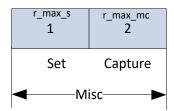

|    | 10.3  | 3.1 Set max state and enable channel           | 64 |

|    | 10.3  | 3.2 "Set" state                                | 65 |

|    | 10.3  | 3.3 "Capture" state                            | 66 |

|    | 10.3  | 3.4 Usage cases                                | 67 |

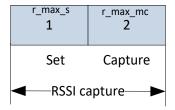

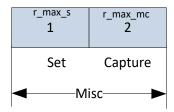

|    | 1     | LO.3.4.1 Case 1: 1-channel sampling for Misc   | 67 |

|    | 1     | LO.3.4.2 Case 2: RSSI capture                  | 67 |

|    | 1     | 10.3.4.3 Case 3 with detailed register setting | 68 |

|    | 10.4  | Register table                                 | 69 |

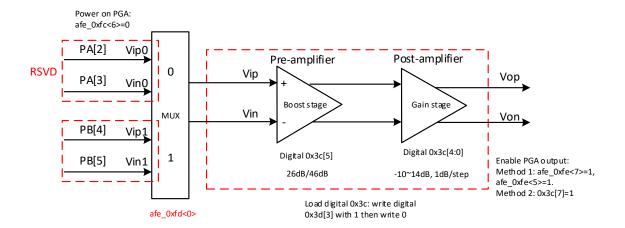

| 13 | L PGA | 4                                              | 72 |

|    | 11.1  | Power on/down                                  | 73 |

|    | 11.2  | Select input channel                           | 73 |

|    | 11.3  | Adjust gain                                    | 73 |

|    | 11.4  | Enable/Disable PGA output                      | 73 |

|    | 11.5  | Load digital register 0x3c                     | 73 |

|    | 11.6  | Register table                                 | 74 |

| 12 | 2 AES |                                                | 75 |

|    | 12.1  | RISC mode                                      | 75 |

|    | 12.2  | AES-CCM                                        | 75 |

|    | 12.3  | Register table                  | 76 |

|----|-------|---------------------------------|----|

| 13 | 8 Key | Electrical Specifications       | 77 |

|    | 13.1  | Absolute maximum ratings        | 77 |

|    | 13.2  | Recommended operating condition | 77 |

|    | 13.3  | Electrical characteristics      | 78 |

|    | 13.4  | General characteristics         | 78 |

|    | 13.5  | Inputs/Outputs characteristics  | 78 |

|    | 13.6  | Pull-up/Pull-down resistor      | 79 |

|    | 13.7  | SPI characteristics             | 80 |

|    | 13.8  | I2C characteristics             | 81 |

|    | 13.9  | RF performance                  | 82 |

|    | 13.10 | Crystal characteristics         | 84 |

|    | 13.11 | RC oscillator characteristics   | 84 |

|    | 13.12 | ADC characteristics             | 84 |

|    | 13.13 | ESD characteristics             | 85 |

|    | 13.14 | Storage condition               | 85 |

| 14 | l App | olication                       | 87 |

|    | 14.1  | Application example for ST17H56 | 87 |

|    | 14.3  | 1.1 Schematic                   | 87 |

|    | 14.1  | 1.2 BOM (Bill of Material)      | 87 |

### 1 Overview

The ST17H56 is -developed BLE SoC solution, which is Bluetooth 4.2 fully standard compliant to allow easy connectivity with Bluetooth Smart Ready mobile phones, tablets, laptops. It supports BLE slave and master mode operations. It also supports BLE 5.0 2Mbps mode and long packet length.

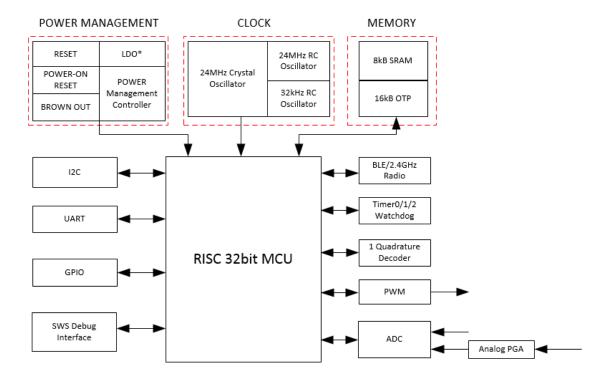

### 1.1 Block diagram

The ST17H56 integrates a power-balanced 32-bit proprietary MCU, a high-performance BLE/2.4GHz Radio, 8kB SRAM, 16kB OTP, a general-purpose ADC, a quadrature decoder (QDEC), 4-channel PWM, flexible I/O interfaces and other peripheral blocks required for Bluetooth Low Energy application development.

The system's block diagram is as shown in Figure 1-1:

Figure 1-1 Block diagram of the system

<sup>\*</sup>Note: The internal LDO regulators serve to supply power for 1.8V digital core and analog modules in Active/Idle/Suspend mode.

### 1.2 Key features

### 1.2.1 General features

General features are as follows:

- 1) 32-bit proprietary microcontroller

- ♦ Better power-balanced performance than ARM MO

- ♦ Instruction cache controller with 2kB cache RAM memory

- ♦ Maximum running speed up to 48MHz

- 2) Memory architecture

- ♦ 16kB OTP

- ♦ 8kB SRAM

- 3) Supports BLE and 2.4GHz proprietary protocols

- 4) RTC and other timers

- Clock source of 24MHz/32kHz RC oscillator, 24MHz crystal oscillator

- ♦ Three general 32-bit timers, with four selectable modes in active mode

- ♦ Watchdog timer

- ♦ A low-frequency 32kHz timer available in low power mode

- 5) Digital and analog interfaces

- ♦ Up to 9 GPIOs

- ♦ Configurable pull-up or pull-down resistors

- ♦ I2C Master/Slave

- ♦ UART interface

- ♦ SWS (Single Wire Slave) interface for debugging

- ♦ One quadrature decoder (QDEC)

- ♦ Up to 4-channel PWM output

- ♦ Up to 5-channel (only GPIO input) ADC with 10.5 ENOB

- ♦ 2-channel differential PGA.

- 6) Hardware AES and random number generator

- 7) Firmware encryption: support software signature based on OTP

- 8) Operating temperature range:  $-40^{\circ}$ C ~+85  $^{\circ}$ C

- 9) Package:

- ♦ 16-pin TSSOP16\_4.96X6.4 mm, ST17H56

- ♦ Completely RoHS-compliant

### 1.2.2 RF Features

RF features include:

- 1) BLE/2.4GHz RF transceiver in worldwide 2.4GHz ISM band

- 2) Bluetooth 4.2 Compliant and BLE 5.0 2Mbps and long packet length

- 3) 2.4GHz proprietary 2Mbps/1Mbps/500kbps/250kbps mode with Adaptive Frequency Hopping support

- 4) Rx Sensitivity: -90dBm @ BLE 1Mbps mode, -86.5dBm @ BLE 2Mbps mode

- 5) Tx Output power: +7dBm

- 6)  $50 \Omega$  matched single-pin antenna input

- 7) RSSI monitoring with +/-4dB accuracy

# 1.2.3 Features of power management module

Features of power management module include:

- 1) Power supply: 1.9V~3.6V

- 2) Battery monitor for low battery voltage detection

- 3) Brownout detection/shutoff and Power-On-Reset

- 4) Multiple-power-state to optimize power consumption

- 5) Low power consumption

- Transmitter mode current: 14.5mA @ 0dBm power, 25mA @ 7dBm power

- Receiver mode current: 13.6mA

- Suspend mode current:

- ♦ IO wakeup: 6.8uA

- ♦ 32kHz RC wakeup: 8uA

- Deep sleep mode current:

# 1.3 Typical application

The ST17H56 can be applied to a variety of Bluetooth Low Energy applications. Typical applications include, but are not limited to:

- HID (Human Interface Devices)

- Gamepad

# 1.4 Ordering information

Table 1-1ST17H56 ordering information

| Product<br>Series | Package Type                      | Temperature<br>Range | Ordering No. | Packing<br>Method | Minimum Order<br>Quantity |

|-------------------|-----------------------------------|----------------------|--------------|-------------------|---------------------------|

| ST17H56           | 16-pin<br>TSSOP16_4.96<br>X6.4 mm | -40℃ ~+85℃           | ST17H56      | Tube              | 9600                      |

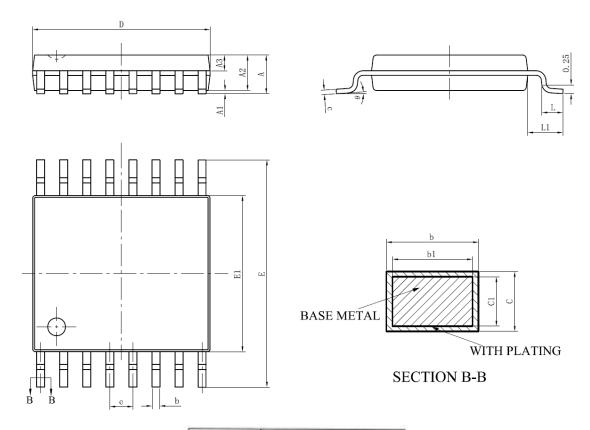

# 1.5 Package

Package dimensions for the ST17H56 are shown as below.

|      | 1.00BSC                                                 |      |  |  |

|------|---------------------------------------------------------|------|--|--|

| 0.45 | 0.60                                                    | 0.75 |  |  |

| (    | 0.65BSC                                                 |      |  |  |

| 4.30 | 4.40                                                    | 4.50 |  |  |

| 6.20 | 6.40                                                    | 6.60 |  |  |

| 4.86 | 4.96                                                    | 5.06 |  |  |

| 0.12 | 0.13                                                    | 0.14 |  |  |

| 0.13 | _                                                       | 0.18 |  |  |

| 0.19 | 0.22                                                    | 0.25 |  |  |

| 0.20 | _                                                       | 0.29 |  |  |

| 0.39 | 0.44                                                    | 0.49 |  |  |

| 0.90 | 1.00                                                    | 1.05 |  |  |

| 0.05 | _                                                       | 0.15 |  |  |

| _    | _                                                       | 1.20 |  |  |

| MIN  | NOM                                                     | MAX  |  |  |

|      | MIN - 0.05 0.90 0.39 0.20 0.19 0.13 0.12 4.86 6.20 4.30 |      |  |  |

Figure 1-2 Package dimension for ST17H56 (Unit: mm)

# 1.6 Pin layout

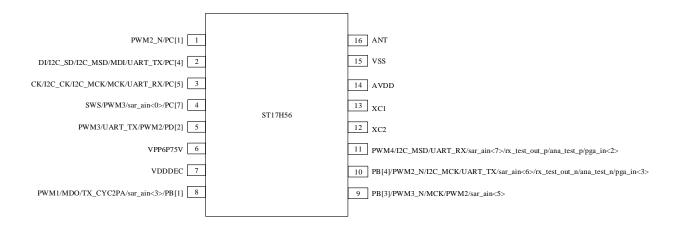

# 1.6.1 Pin layout for ST17H56

The figure below shows pin assignment for the ST17H56.

Figure 1-3 Pin assignment for ST17H56

Functions of 16 pins for the ST17H56 are described in the table below:

Table 1-2Pin functions for ST17H56

| No. | Pin Name                                                                       | Туре        | Description                                                                                                            |

|-----|--------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------|

| 1   | PWM2_N/PC[1]                                                                   | Digital I/O | PWM2 inverting output /GPIO PC[1]                                                                                      |

| 2   | DI/I2C_SD/I2C_MSD/MDI/UART_TX/PC[4]                                            | Digital I/O | SPI Slave data input / I2C Slave serial data / I2C  Master serial data / SPI Master data input /  UART_TX / GPIO PC[4] |

| 3   | CK/I2C_CK/I2C_MCK/MCK/UART_RX/PC[5]                                            | Digital I/O | SPI Slave clock / I2C Slave clock / I2C Master clock / SPI Master clock / UART_RX / GPIO PC[5]                         |

| 4   | SWS/PWM3/sar_ain<0>/PC[7]                                                      | Digital I/O | Single wire slave / PWM3 output / SAR ADC input / GPIO PC[7]                                                           |

| 5   | PWM3/UART_TX/PWM2/PD[2]                                                        | Digital I/O | PWM3 output / UART_TX / PWM2 output / GPIO PD[2]                                                                       |

| 6   | VPP6P75V                                                                       | PWR         | 6.75V supply for OTP programming                                                                                       |

| 7   | VDDDEC                                                                         | PWR         | Digital LDO output                                                                                                     |

| 8   | PWM1/MDO/TX_CYC2PA/sar_ain<3>/PB[1]                                            | Digital I/O | PWM1 output/MDO/ MDO/TX_CYC2PA/SAR ADC input/ GPIO PB[1]                                                               |

| 9   | PWM3_N/MCK/PWM2/sar_ain<5>/PB[3]                                               | Digital I/O | PWM3 inverting output/MCK/PWM2 output/SAR ADC input/GPIO PB[3]                                                         |

| 10  | PWM2_N/I2C_MCK/UART_TX/sar_ain<6>/r<br>x_test_out_n/ana_test_n/pga_in<3>/PB[4] | Digital I/O | PWM2 inverting output / I2C Master clock / UART_TX / SAR ADC input / PGA input / GPIO PB[4]                            |

| 11  | PWM4/I2C_MSD/UART_RX/sar_ain<7>/rx_t est_out_p/ana_test_p/pga_in<2>/PB[5]      | Digital I/O | PWM4 output / I2C Master serial data / UART_RX / SAR ADC input / PGA input / GPIO PB[5]                                |

| 12  | XC2                                                                            | Analog      | 24MHz crystal input                                                                                                    |

| No. | Pin Name | Туре       | Description               |

|-----|----------|------------|---------------------------|

| 13  | XC1      | Analog     | 24MHz crystal input       |

| 14  | AVDD     | PWR        | 3V output                 |

| 15  | VSS      | GND        | ground for the whole chip |

| 16  | ANT      | Analog I/O | RF antenna                |

### 1.6.2 Notes

- 1) All digital IOs including PB[1], PB[3], PB[4], PB[5], PC[1], PC[4], PC[5], PC[7], and PD[2] can be used as GPIOs and have configurable pull-up/pull-down resistor.

- 2) I2C Master/Slave pins can be configured independently.

- ♦ Pins marked with I2C\_MCK and I2C\_MSD can be configured as I2C Master clock and serial data.

- ♦ Pins marked with I2C\_CK and I2C\_SD can be configured as I2C Slave clock and serial data.

- 3) UART: UART\_TX, UART\_RX.

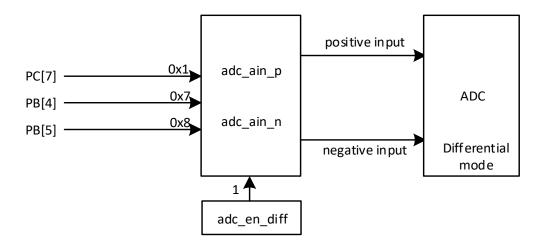

- 4) ADC input: PC[7], PB[4], PB[5]. Please refer to section 10 SAR ADC.

- 5) Analog PGA input: PB[4], PB[5]. Please refer to section 11 PGA.

- 6) Pin drive strength: All GPIOs support drive strength up to 8mA (8mA when "DS"=1, 4mA when "DS"=0). Please refer to section **7.1.1** Basic configuration for the corresponding "DS" register address and the default setting.

# 2 Memory and MCU

# 2.1 Memory

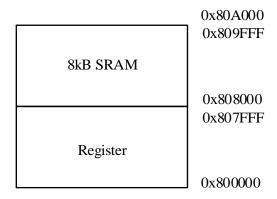

The ST17H56 embeds 8kB SRAM and 16kB OTP.

# 2.1.1 SRAM/Register

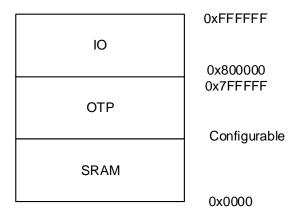

SRAM/Register memory map is shown as follows:

Figure 2-1 Physical memory map

Register address: 0x800000 ~ 0x807FFF; 8kB SRAM address: 0x808000 ~ 0x809FFF.

Both register and 8kB SRAM address can be accessed (read or write) via debugging interface (I2C, SWS interface).

# 2.1.2 OTP

OTP address mapping is configurable.

Figure 2-2 MCU memory map

### 2.2 Firmware encryption

The ST17H56 supports Bootloader-based firmware encryption/decryption.

The firmware can be encrypted using a customer-provided security key. The customer security key is written into a specified location within the internal OTP (i.e. the last 4-bytes of the OTP), and becomes unreadable. Any attempt to read the key will only result in either all 1's or all 0's.

The encrypted firmware can be generated based on the plaintext firmware and the customer security key. The customer can burn the security key into the obscured memory area and also the encrypted firmware into the OTP.

The firmware is readable by all, but appears as garbled binaries to 3rd party.

### 2.3 MCU

The ST17H56 integrates a powerful 32-bit MCU. The digital core is based on 32-bit RISC, and the length of instructions is 16 bits; four hardware breakpoints are supported.

### 2.4 Working modes

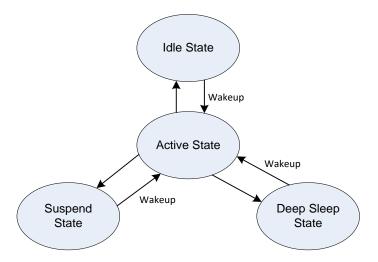

The ST17H56 has four working modes: Active, Idle, Suspend and Deep Sleep. This section mainly gives the description of every working mode and mode transition.

Figure 2-3 Transition chart of working modes

# 2.4.1 Active mode

In active mode, the MCU block is at working state, and the ST17H56 can transmit or receive data via its embedded RF transceiver. The RF transceiver can also be powered down if no data transfer is needed.

### 2.4.2 Idle mode

In Idle mode, the MCU block stalls, and the RF transceiver can be at working state or be powered down. The time needed for the transition from Idle mode to Active mode is negligible.

### 2.4.3 Power-saving mode

For the ST17H56, there are two kinds of power-saving modes: suspend mode and deep sleep mode. The two modes have similar transition sequences but different register settings. For 1.8V digital core, it's still provided with the working power by 1.8V LDO in suspend mode; while in deep sleep mode, the 1.8V LDO will be turned off, and the digital core is powered down.

In suspend mode, the RF transceiver is powered down, and the clock of the MCU block is stopped.

While in deep sleep mode, both the RF transceiver and the MCU block are powered down with only power management block being active.

Deep sleep mode includes two sub-modes, including deep sleep with SRAM retention and deep sleep without SRAM retention.

| Deep Sleep Sub-Mode Characteristic                | Deep sleep with SRAM retention                                    | Deep sleep without SRAM retention |

|---------------------------------------------------|-------------------------------------------------------------------|-----------------------------------|

| Wakeup time to Active mode                        | Shorter than deep sleep without retention, almost same as Suspend | 1ms                               |

| 8kB retention SRAM (with retention in deep sleep) | full                                                              | off                               |

Table 2- 1Deep sleep sub modes

# \*Note:

- "full": Full speed. In Active, Idle and Suspend mode, the 8kB retention SRAM is powered on and work normally (can be accessed); in Deep sleep with SRAM retention, the retention SRAM is powered on, however, the contents of the retention SRAMs can be retained and cannot be accessed.

- 2) "off": The retention SRAM is powered down in Deep sleep without SRAM retention.

$T_{SP2A}$ : the transition time needed for the ST17H56 to enter the active mode from suspend mode.

T<sub>DS2A</sub>: the transition time needed from deep sleep mode to active mode.

For the tested values of the " $T_{SP2A}$ " and " $T_{DS2A}$ ", please refer to section General characteristics.

Table 2- 2 Retention analog registers in deep sleep

| Address  | R/W | Description                                 | Default value |

|----------|-----|---------------------------------------------|---------------|

| afe_0x34 | R/W | buffer, watchdog reset/software reset clean | 0x00          |

| afe_0x35 | R/W | buffer, watchdog reset/software reset clean | 0x00          |

| afe_0x36 | R/W | buffer, watchdog reset/software reset clean | 0x00          |

| afe_0x37 | R/W | buffer, watchdog reset/software reset clean | 0x00          |

| afe_0x38 | R/W | buffer, watchdog reset/software reset clean | 0x00          |

| afe_0x39 | R/W | buffer, watchdog reset/software reset clean | 0xff          |

| afe_0x3a | R/W | buffer, only power on reset clean           | 0x00          |

| afe_0x3b | R/W | buffer, only power on reset clean           | 0x00          |

| afe_0x3c | R/W | buffer, only power on reset clean           | 0x00          |

| afe_0x3d | R/W | buffer, only power on reset clean           | 0x00          |

| afe_0x3e | R/W | buffer, only power on reset clean           | 0x00          |

| afe_0x3f | R/W | buffer, only power on reset clean           | 0x7f          |

Analog registers (afe\_0x34  $\sim$  afe\_0x3f) as shown above are retained in deep sleep mode and can be used to store program state information across deep sleep cycles.

- ♦ Analog registers afe\_0x3a~ afe\_0x3f are non-volatile even when chip enters deep sleep or chip is reset by watchdog or software, i.e. the contents of these registers won't be changed by deep sleep or watchdog reset or chip software reset.

- ♦ Analog registers afe\_0x34~ afe\_0x39 are non-volatile in deep sleep, but will be cleared by watchdog reset or chip software reset.

- ♦ After POR (Power-On-Reset), all registers will be cleared to their default values, including these analog registers.

User can set flag in these analog registers correspondingly, so as to check the booting source by reading the flag.

For chip software reset, please refer to **section 2.5 Reset**.

# 2.5 Reset

The chip supports three types of reset methods, including POR (Power-On-Reset), watchdog reset and software reset.

- 1) POR: After power on, the whole chip will be reset, and all registers will be cleared to their default values.

- 2) Watchdog reset: A programmable watchdog is supported to monitor the system. If watchdog reset is triggered, registers except for retention analog registers afe\_0x3a~ afe\_0x3f will be cleared.

- 3) Software reset: It is also feasible to carry out software reset for the whole chip or some modules.

- Setting address 0x6f[5] to 1b'1 is to reset the whole chip. Similar to watchdog reset (see section 2.4.3 Power-saving mode), retention analog registers afe\_0x3a~ afe\_0x3f are non-volatile, while other registers including afe\_0x34~ afe\_0x39 will be cleared by chip software reset.

- ♦ Addresses 0x60~0x62 serve to reset individual modules: if some bit is set to logic "1", the corresponding module is reset.

Table 2- 3 Register configuration for software reset

| Address | Mnemonic    | Туре    | Description                             | Reset Value |

|---------|-------------|---------|-----------------------------------------|-------------|

|         |             |         | Reset control, 1 for reset, 0 for clear |             |

|         |             |         | [0]: SPI                                |             |

|         |             |         | [1]: I2C                                |             |

|         |             |         | [2]: n/a                                |             |

| 0x60    | RST0        | R/W     | [3]: n/a                                | 0xc0        |

|         |             |         | [4]: MCU                                |             |

|         |             |         | [5]: n/a                                |             |

|         |             |         | [6]: AIF                                |             |

|         |             |         | [7]: ZB                                 |             |

|         | 51 RST1 R/V |         | [0]: system_timer                       |             |

|         |             | T1 R/W  | [1]: algm                               |             |

|         |             |         | [2]: dma                                |             |

| 0x61    |             |         | [3]: rs232                              | 0x3f        |

| 0.01    | 1/311       | 11,7 00 | [4]: pwm                                | 0.51        |

|         |             |         | [5]: aes                                |             |

|         |             |         | [6]: n/a                                |             |

|         |             |         | [7]: swires                             |             |

|         |             |         | [0]: n/a                                |             |

|         |             |         | [1]: n/a                                |             |

| 0x62    | RST2        | R/W     | [2]: n/a                                | 0x88        |

| 0,02    | 11312       | 11,700  | [3]: adc                                | 0,00        |

|         |             |         | [4]: mcic                               |             |

|         |             |         | [5]: soft reset to reset mcic enable    |             |

| Address | Mnemonic | Туре | Description                               | Reset Value |

|---------|----------|------|-------------------------------------------|-------------|

|         |          |      | [6]: rsvd (mspi)                          |             |

|         |          |      | [7]: alg                                  |             |

|         |          |      | [0]: suspend enable                       |             |

| 0x6f    |          |      | [5]: rst all (act as watchdog reset)      |             |

|         | PWDNFN   | W    | [6]: rsvd (mcu low power mode)            | 0x00        |

|         | PWDINEIN |      | [7]: stall mcu trig If bit[0] set 1, then | 0x00        |

|         |          |      | system will go to suspend. Or only        |             |

|         |          |      | stall mcu.                                |             |

### 2.6 Power Management

The multiple-stage Power Management (PM) module is flexible to control power state of the whole chip or individual functional blocks such as MCU, RF Transceiver, and peripherals.

# 2.6.1 Digital LDO

The chip embeds LDO regulators to generate 1.8V regulated voltage. The internal LDO regulators serve to supply power for 1.8V digital core and analog modules in Active/Idle/Suspend mode.

While in deep sleep mode, the embedded 1.8V LDO regulators will be turned off.

# 2.6.2 VBUS LDO

The embedded VBUS LDO generates 3.0V voltage to supply power for the whole chip. The VBUS LDO supports two working modes, including LDO mode and Bypass mode.

- ♦ When the input voltage VBAT is 3.3V~4.3V, the VBUS LDO works in LDO mode.

- ♦ When the input voltage VBAT is lower than 3.3V, the VBUS LDO works in Bypass mode, and its output voltage is the same as VBAT input voltage.

# 2.6.3 Power-On-Reset (POR) and Brown-out detect

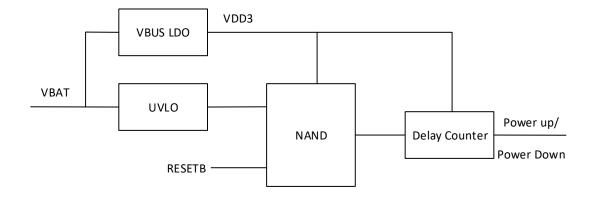

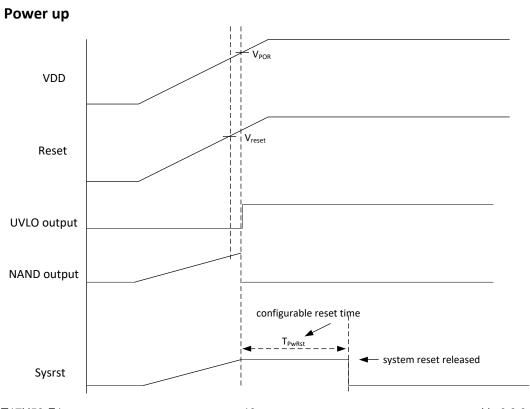

Figure 2- 4 Block diagram for power up/down

The whole chip power up and down is controlled by the UVLO (Ultra-low Voltage Lockout) module and the external RESETB pin via the logic shown in the above diagram. UVLO takes the external power supply as input and releases the lock only when the power supply voltage is higher than a preset threshold. The RESETB pin has an internal pull-up resistor; an external Cap can be connected on the RESETB pin to control the POR delay.

After both UVLO and RESETB release, there is further configurable **delay** before the system reset signal ("**Sysrst**") is released. This delay is adjusted by analog register afe\_0x20. Since the content of afe\_0x20 is reset to default only after power cycle, watchdog reset, or software reset, the delay change using afe\_0x20 is only applicable when the chip has not gone through these reset conditions. For example, after deep sleep wakeup, the setting in afe\_0x20 will take effect.

Address Description Default

r\_dly:

[6:0]: delay, 32kHz decrease counter. Default delay 1ms.

[7] rsvd

Oxe0

Table 2- 4Analog register to control delay counter

<sup>\*</sup>Note: The register afe\_0x20 will be reset to default after power cycle (POR), watchdog reset, or software reset.

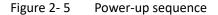

Figure 2- 6 Power-down sequence

The power up and power down sequence is shown in Table 13- 4, with the following parameters:

$\diamondsuit$  V<sub>POR</sub>: VDD voltage when V<sub>UVLO</sub> turns to high level

♦ V<sub>Pdn</sub>: VDD voltage when V<sub>UVLO</sub> turns to low level

♦ T<sub>PwRst</sub>: Delay counter value (Configurable via analog register afe\_0x20)

# 2.6.4 Working mode switch

The chip can switch to idle mode to stall the MCU.

To minimize power consumption, the chip can switch to power saving mode (suspend or deep sleep) correspondingly. In this case, the low-power 32kHz RC oscillator can still be running, and the low frequency wakeup timer LTIMER can be programmed to stay alive. The device can be activated to working state via external pin trigger or internal wakeup timer.

User can directly invoke corresponding library function to switch working mode of the chip.

If certain module doesn't need to work, user can power down this module in order to save power.

Table 2-5 Analog registers for module power up/down control

| Address     | Local name     | Default Value | Description                                                       |

|-------------|----------------|---------------|-------------------------------------------------------------------|

| afe_0x05<0> | 32K_rc_pd      | 0             | Power down 32kHz RC oscillator 1: Power down 0: Power up          |

| afe_0x05<2> | 24M_rc_pd      | 0             | Power down of 24MHz RC oscillator 1: Power down 0: Power up       |

| afe_0x05<3> | xtal_LDO_pd    | 0             | Power down of 24MHz crystal oscillator 1: Power down 0: Power up  |

| afe_0x05<4> | ldo_ana_pd     | 0             | Power down of analog LDO  1: Power down  0: Power up              |

| afe_0x06<1> | rx_lnaLDO_pd   | 1             | Power down LNA LDO in RF transceiver  1: Power down  0: Power up  |

| afe_0x06<2> | rx_anaLDO_pd   | 1             | Power down analog LDO in RF transceiver 1: Power down 0: Power up |

| afe_0x06<3> | rx_rfLDO_pd    | 1             | Power down RF LDO in RF transceiver 1: Power down 0: Power up     |

| afe_0x06<6> | pll_vco_ldo_pd | 1             | Power down VCO LDO 1: Power down 0: Power up                      |

### 2.7 Wakeup sources

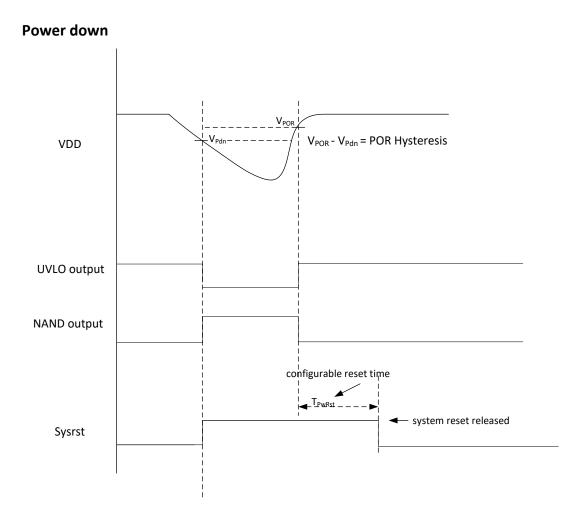

Figure 2-7 Wakeup sources

### 2.7.1 Wakeup source – 32kHz timer

This wakeup source is able to wake up the system from suspend mode or deep sleep mode. Address afe\_0x26 bit[6] is the enabling bit for wakeup source from 32kHz timer.

# 2.7.2 Wakeup source – IO

This wakeup source is able to wake up the system from suspend mode or deep sleep mode. And IO wakeup supports high level or low level wakeup which is configurable via wakeup polarity control registers. Total wakeup pin can be up to 11.

Address afe\_0x26[4] should be set as 1b'1 to enable IO wakeup source.

Enabling control registers: PB[7:0] enabling control register is afe\_0x28[7:0].

Polarity control registers: PB[7:0] polarity control register is afe\_0x22[7:0].

The corresponding driver is available so that user can directly invoke it to use IO wakeup source.

# 2.7.3 Register table

Table 2- 6 Analog registers for Wakeup

| Address     | R/W | Description                                                  | Default Value |

|-------------|-----|--------------------------------------------------------------|---------------|

|             |     | pa_polarity:                                                 |               |

| afe_0x21    | R/W | [7:5]: rsvd (select polarity for PA[7]~PA[5] IO (pad) wakeup | 0x00          |

|             |     | 0: high level, 1: low level)                                 |               |

|             |     | pb_polarity:                                                 |               |

|             |     | [7:0]: select polarity for PB[7]~PB[0] IO (pad) wakeup       |               |

| afe_0x22    | R/W | [5:3]: PB[5]~PB[3]                                           | 0x00          |

|             |     | [1]: PB[1]                                                   |               |

|             |     | 0: high level, 1: low level                                  |               |

| afe_0x26[3] | R/W | Enable/Mask filter for IO (Pad) wakeup                       | 0x00          |

| Address     | R/W      | Description                                                    | Default Value |

|-------------|----------|----------------------------------------------------------------|---------------|

|             |          | 1: Select 16us filter to filter out jitter on IO PAD input.    |               |

|             |          | 0: IO Pad combinational logic output (disable filter)          |               |

| afe_0x26[4] | R/W      | 1: Enable IO (pad) wakeup                                      |               |

| afe_0x26[5] | R/W      | Rsvd (Enable digital core wakeup)                              |               |

| afe_0x26[6] | R/W      | 1: Enable 32kHz timer wakeup                                   |               |

|             |          | pad_wkup_pa_en:                                                |               |

| afe_0x27    | R/W      | [7:5]: rsvd (enable/disable PA[7]~PA[5] IO (pad) wakeup        | 0x00          |

|             |          | 1: enable; 0: disable)                                         |               |

|             |          | pad_wkup_pb_en:                                                |               |

|             |          | [7:0]: enable/disable PB[7]~PB[0] IO (pad) wakeup              |               |

| afe_0x28    | R/W      | [5:3]: PB[5]~PB[3]                                             | 0x00          |

|             |          | [1]: PB[1]                                                     |               |

|             |          | 1: enable; 0: disable                                          |               |

|             |          | State flag bits                                                |               |

|             |          | [1]: pm_irq, i.e. 32kHz timer wakeup status                    |               |

|             | 0x44 W1C | [2]: rsvd (digital core wakeup status)                         |               |

| afe_0x44    |          | [3] wkup_pad, i.e. IO (pad) wakeup status.                     | 0x00          |

|             |          | Write 1 to clean.                                              |               |

|             |          | e.g. If bit[3] is 1, it indicates the system is waked up by IO |               |

|             |          | (pad) source.                                                  |               |

Table 2-7 Digital register for Wakeup

| Address | Mnemonic | Туре | Description                                                                                                                                                                                                                                                       | Reset Value |

|---------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 0x6e    | WAKEUPEN | R/W  | Wakeup enable  [0]: rsvd (enable wakeup from I2C host)  [1]: rsvd (enable wakeup from SPI host)  [2]: rsvd  [3]: enable wakeup from gpio  [4]: rsvd (enable wakeup from QDEC synchronous interface)  System resume control  [7]: sleep wakeup reset system enable | 1f          |

### 3 BLE/2.4G RF Transceiver

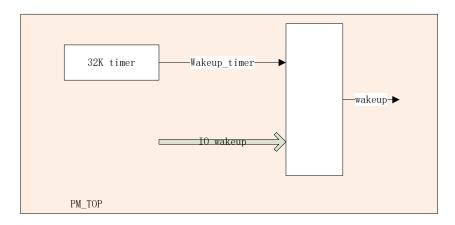

### 3.1 Block diagram

The ST17H56 integrates an advanced BLE/2.4GHz RF transceiver. The RF transceiver works in the worldwide 2.4GHz ISM (Industrial Scientific Medical) band and contains an integrated Balun with a single-ended RF Tx/Rx port pin. No matching components are needed.

The transceiver consists of a fully integrated frequency synthesizer, a power amplifier, a modulator and a receiver. The transceiver can be configured to work in Bluetooth 4.2 standard-compliant 1Mbps BLE mode, BLE 5.0 2Mbps mode, and 2.4GHz proprietary 2Mbps/1Mbps/500kbps/250kbps mode. All modes support FSK/GFSK/MSK modulations.

Figure 3-1 Block diagram of RF transceiver

The internal PA can deliver a maximum 7dBm output power without the needs for an external RF PA. If higher output power is needed, then an external RF Frontend can be added to boost the output power.

### 3.2 Function description

### 3.2.1 Air interface data rate and RF channel frequency

Air interface data rate, the modulated signaling rate for RF transceiver when transmitting and receiving data, is configurable via related register setting: 250kbps, 500kbps, 1Mbps, 2Mbps.

For the ST17H56, RF transceiver can operate with frequency ranging from 2.400GHz to 2.4835GHz. The RF channel frequency setting determines the center of the channel.

### 3.3 Baseband

The baseband is disabled by default. The corresponding API is available for user to power on/down the baseband and enable/disable clock, so that the baseband can be turned on/off flexibly.

The baseband contains dedicated hardware logic to perform fast AGC control, access code correlation, CRC checking, data whitening, encryption/decryption and frequency hopping logic.

The baseband supports all features required by Bluetooth V4.2 specification. It also supports BLE 5.0 2Mbps mode and long packet length.

#### 3.3.1 **Packet format**

Packet format in standard 1Mbps BLE mode is shown as Table 3-1:

Table 3-1 Packet Format in standard 1Mbps BLE mode

| LSB       |                |                  | MSB        |

|-----------|----------------|------------------|------------|

| Preamble  | Access Address | PDU              | CRC        |

| (1 octet) | (4 octets)     | (2 ~ 257 octets) | (3 octets) |

Packet length 80bit ~ 2120bit (80~2120us @ 1Mbps).

Packet format in standard 2Mbps BLE mode is shown as Table 3-2:

Table 3- 2 Packet format in standard 2Mbps BLE mode

| LSB        |                |                  | MSB        |

|------------|----------------|------------------|------------|

| Preamble   | Access Address | PDU              | CRC        |

| (2 octets) | (4 octets)     | (2 ~ 257 octets) | (3 octets) |

Packet format in 2.4GHz Proprietary mode is shown as Table 3-3:

Table 3-3 Packet format in Proprietary mode

| LSB      |                          |                             | MSB         |

|----------|--------------------------|-----------------------------|-------------|

| Preamble | Address code             | Packet Controller + Payload | CRC         |

| (8 bits) | (configurable 3~5 bytes) | (1~63 bytes)                | (1~2 bytes) |

#### 3.3.3 **RSSI** and frequency offset

The ST17H56 provides accurate RSSI (Receiver Signal Strength Indicator) and frequency offset indication.

- 1Byte RSSI can be read upon receiving the data packet.

- If no data packet is received (e.g. to perform channel energy measurement when no desired signal is present), real-time RSSI can also be read from specific registers which will be updated automatically.

- RSSI resolution can reach +/-4dB.

- 2-Byte Frequency offset value can be read upon receiving the data packet. Valid bits of actual frequency offset may be less than 16bits, and different valid bits correspond to different tolerance range.

supplies corresponding drivers for user to read RSSI and frequency offset as needed.

### 4 Clock

### 4.1 Clock sources

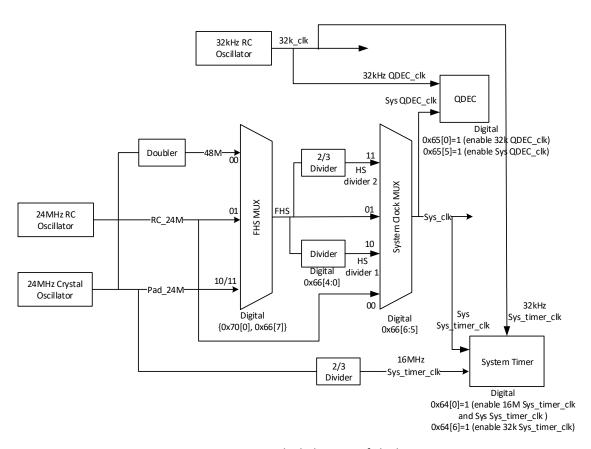

Figure 4-1 Block diagram of clock

The ST17H56 clock supports 24MHz external crystal or 24MHz/32kHz embedded RC oscillator.

- ♦ A RC\_24M clock is available from an embedded 24MHz RC oscillator. It can be directly used as clock source for system, and it's also a selectable source for high speed clock (FHS). When system clock is configured as 24MHz RC (default), the RC\_24M clock can be output to PA[7] by configuring the digital registers as below: 0x586=0x7f, 0x5a9=0x40.

- ♦ A RC\_32k clock is available from an embedded 32kHz RC oscillator. It can provide a 32kHz clock source for 32kHz timer during sleep state as well as System Timer and QDEC module. When 32kHz clock is configured as 32kHz RC (default), the RC\_32k clock can be output to PA[1] by configuring the digital registers as below: 0x586=0xfd, 0x5a8=0x08.

- ♦ A Pad\_24M clock is available from external 24MHz crystal via pin XC1 and XC2. It can provide 16MHz clock source for System Timer via a 2/3 frequency divider. The Pad\_24M can be directly used as clock source for high speed clock (FHS), or generate a 48MHz clock source via a frequency doubler for FHS.

- → High speed clock (FHS) can be directly used as clock source for system, or generate HS divider clock 1 or 2 source via a configurable or fixed 2/3 frequency divider for system.

### 4.2 System clock

There are four selectable clock sources for MCU system clock: **RC\_24M** (derived from 24MHz RC oscillator), High speed clock "**FHS**", **HS divider clock 1** (derived from "FHS" via a configurable frequency divider), **HS divider clock 2** (derived from "FHS" via a fixed 2/3 frequency divider).

The high speed clock (FHS) is selectable via address {0x70[0], 0x66[7]} from the following sources: **48MHz** clock (derived from 24MHz crystal oscillator via a frequency doubler), **RC\_24M** (derived from 24MHz RC oscillator), and **Pad\_24M** (derived from 24MHz crystal oscillator).

The digital register CLKSEL (address 0x66) serves to set system clock: System clock source is selectable via bit[6:5].

- ♦ If address 0x66[6:5] is set to 2b'00 to select the RC\_24M, system clock frequency equals 24MHz.

- ♦ If address 0x66[6:5] is set to 2b'01 to select the FHS clock, system clock frequency equals the FHS frequency (F<sub>FHS</sub>).

- ♦ If address 0x66[6:5] is set to 2b'10 to select the HS divider clock 1, system clock frequency is adjustable via address 0x66[4:0]. The formula is shown as below:

- $F_{System clock} = F_{FHS} / (system clock divider value in address 0x66[4:0]).$

- ♦ If address 0x66[6:5] is set to 2b'11 to select the HS divider clock 2, system clock frequency equals F<sub>FHS</sub> \* 2/3.

### 4.3 Module clock

Registers CLKEN0~CLKEN2 (address 0x63~0x65) are used to enable or disable clock for various modules. By disable the clocks of unused modules, current consumption could be reduced.

### 4.3.1 System Timer clock

System Timer simultaneously uses system clock, a 16MHz clock, as well as a 32kHz clock.

- ♦ The 16MHz clock is derived from 24MHz crystal oscillator via a 2/3 frequency divider.

- ♦ The 32kHz clock is RC\_32k.

- → Digital register 0x64 bit[0] and bit[6] should be enabled to drive the System Timer by the 16MHz clock, system clock, as well as the 32kHz clock.

### 4.3.2 QDEC clock

QDEC module simultaneously uses system clock as well as a 32kHz clock.

- ♦ The 32kHz clock is RC\_32k.

- ♦ Digital register 0x65 bit[0] and bit[5] should be enabled to drive the whole QDEC module by the 32kHz clock and system clock.

# 4.4 Register table

Table 4- 1 Register table related to clock

| Address | Mnemonic         | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Default |  |

|---------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

|         | Digital register |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |  |

| 0x63    | CLKENO           | R/W | Clock enable control: 1 for enable; 0 for disable  [0]: SPI  [1]: I2C  [2]: HOSTIRQ  [3]: n/a  [4]: MCU  [5]: FPU (Float Point Unit)  [6]: AIF  [7]: ZB                                                                                                                                                                                                                                                                                                                        |         |  |

| 0x64    | CLKEN1           | R/W | Clock enable control: 1 for enable; 0 for disable  [0]: System timer (16M_clk and sys_clk for System timer)  [1]: ALGM  [2]: DMA  [3]: RS232  [4]: PWM  [5]: AES  [6]: 32k_clk for system timer  [7]: Swires                                                                                                                                                                                                                                                                   | 80      |  |

| 0x65    | CLKEN2           | R/W | Clock enable control: 1 for enable; 0 for disable  [0]: 32k_clk for QDEC  [1]: 32k_clk for PWM  [2:3]: n/a  [4]: MCIC  [5]: QDEC (sys_clk for QDEC)  [6:7]: n/a                                                                                                                                                                                                                                                                                                                | 10      |  |

| 0x66    | CLKSEL           | R/W | System clock select [4:0]: system clock divider.  If 0x66[6:5] is set as 2b' 10, F <sub>Sysclk</sub> = F <sub>FHS</sub> / CLKSEL[4:0].  FHS: refer to 0x70 FHS_sel. [6:5]: select system clock source 2'b00: RC_24M from RC oscillator 2'b01: FHS clock (High speed clock) 2'b10: HS divider clock 1 derived from FHS clock via a configurable divider (see 0x66[4:0]) 2'b11: HS divider clock 2 derived from FHS clock via a fixed 2/3 divider {0x70[0], 0x66[7]}: FHS select | 06      |  |

| 0x70    | FHS_sel          | R/W | {0x70[0], 0x66[7]}: FHS select 2'b00: 48MHz clock doubled from 24MHz crystal oscillator 2'b01: RC_24M from RC oscillator 2'b1x: Pad_24M from 24MHz crystal oscillator                                                                                                                                                                                                                                                                                                          | 00      |  |

### 5 Timers

# 5.1 Timer0~Timer2

The ST17H56 supports three general 32-bit timers in active mode, including Timer0~ Timer2. All of the three timers support four modes: Mode 0 (System Clock Mode), Mode 1 (GPIO Trigger Mode), Mode 2 (GPIO Pulse Width Mode) and Mode 3 (Tick Mode), which are selectable via the register TMR\_CTRL0 (address 0x620) ~ TMR\_CTRL1 (address 0x621).

Timer 2 can also be configured as "watchdog" timer to monitor firmware running.

# 5.1.1 Register table

Table 5-1 Register configuration for Timer0~Timer2

| 1able 5- 1 Register configuration for TimerU~Timer2 |             |      |                                         |                |

|-----------------------------------------------------|-------------|------|-----------------------------------------|----------------|

| Address                                             | Mnemonic    | Туре | Description                             | Reset<br>Value |

| 0x72                                                | Wd_status   | R/W  | [0] watch dog status, write 1 to clear. | 00             |

|                                                     |             |      | [0]Timer0 enable                        |                |

|                                                     |             |      | 1: enable                               |                |

|                                                     |             |      | [2:1] Timer0 mode.                      |                |

|                                                     |             |      | 0: using sclk, 1: using gpio,           |                |

| 0x620                                               | TMR_CTRL0   | RW   | 2: count width of gpi, 3: tick          | 00             |

|                                                     |             |      | [3]Timer1 enable                        |                |

|                                                     |             |      | [5:4] Timer1 mode.                      |                |

|                                                     |             |      | [6]Timer2 enable                        |                |

|                                                     |             |      | [7]Bit of timer2 mode                   |                |

| 0x621                                               | TMD CTDL1   | RW   | [0]Bit of timer2 mode                   | 00             |

| UXOZI                                               | TMR_CTRL1   | NVV  | [7:1]Low bits of watch dog capture      | 00             |

|                                                     |             |      | [6:0]High bits of watch dog capture.    |                |

|                                                     |             |      | Watch dog capture is compared with      |                |

| 0x622                                               | TMR_CTRL2   | RW   | [31:18] of timer2 ticker.               | 00             |

|                                                     |             |      | [7]watch dog capture enable             |                |

|                                                     |             |      | 1: enable                               |                |

|                                                     |             |      | [0] timer0 status, write 1 to clear     |                |

| 0x623                                               | TMR_STATUS  | RW   | [1] timer1 status, write 1 to clear     | 00             |

|                                                     |             |      | [2] timer2 status, write 1 to clear     |                |

| 0x624                                               | TMR_CAPT0_0 | RW   | Byte 0 of timer0 capture                | 00             |

| 0x625                                               | TMR_CAPT0_1 | RW   | Byte 1 of timer0 capture                | 00             |

| 0x626                                               | TMR_CAPT0_2 | RW   | Byte 2 of timer0 capture                | 00             |

| 0x627                                               | TMR_CAPT0_3 | RW   | Byte 3 of timer0 capture                | 00             |

| 0x628                                               | TMR_CAPT1_0 | RW   | Byte 0 of timer1 capture                | 00             |

| 0x629                                               | TMR_CAPT1_1 | RW   | Byte 1 of timer1 capture                | 00             |

| 0x62a                                               | TMR_CAPT1_2 | RW   | Byte 2 of timer1 capture                | 00             |

| 0x62b                                               | TMR_CAPT1_3 | RW   | Byte 3 of timer1 capture                | 00             |

| 0x62c                                               | TMR_CAPT2_0 | RW   | Byte 0 of timer2 capture                | 00             |

| 0x62d                                               | TMR_CAPT2_1 | RW   | Byte 1 of timer2 capture                | 00             |

| 0x62e                                               | TMR_CAPT2_2 | RW   | Byte 2 of timer2 capture                | 00             |

| 0x62f                                               | TMR_CAPT2_3 | RW   | Byte 3 of timer2 capture                | 00             |

|                                                     | <b>_</b>    | •    |                                         |                |

| Address | Mnemonic    | Туре | Description             | Reset<br>Value |

|---------|-------------|------|-------------------------|----------------|

| 0x630   | TMR_TICKO_0 | RW   | Byte 0 of timer0 ticker | 00             |

| 0x631   | TMR_TICK0_1 | RW   | Byte 1 of timer0 ticker | 00             |

| 0x632   | TMR_TICK0_2 | RW   | Byte 2 of timer0 ticker | 00             |

| 0x633   | TMR_TICK0_3 | RW   | Byte 3 of timer0 ticker | 00             |

| 0x634   | TMR_TICK1_0 | RW   | Byte 0 of timer1 ticker | 00             |

| 0x635   | TMR_TICK1_1 | RW   | Byte 1 of timer1 ticker | 00             |

| 0x636   | TMR_TICK1_2 | RW   | Byte 2 of timer1 ticker | 00             |

| 0x637   | TMR_TICK1_3 | RW   | Byte 3 of timer1 ticker | 00             |

| 0x638   | TMR_TICK2_0 | RW   | Byte 0 of timer2 ticker | 00             |

| 0x639   | TMR_TICK2_1 | RW   | Byte 1 of timer2 ticker | 00             |

| 0x63a   | TMR_TICK2_2 | RW   | Byte 2 of timer2 ticker | 00             |

| 0x63b   | TMR_TICK2_3 | RW   | Byte 3 of timer2 ticker | 00             |

### 5.1.2 Mode0 (System Clock Mode)

In Mode 0, system clock is used as clock source.

After Timer is enabled, Timer Tick (i.e. counting value) is increased by 1 on each positive edge of system clock from preset initial Tick value. Generally the initial Tick value is set as 0.

Once current Timer Tick value matches the preset Timer Capture (i.e. timing value), Timer stops counting, Timer status is updated, and an interrupt is generated (if enabled).

Following is an example to show steps of setting TimerO as Mode O.

### 1st: Set initial Tick value of Timer0

Set initial Tick value of Timer0 via registers TMR\_TICKO\_0~TMR\_TICKO\_3 (address 0x630~0x633). Address 0x630 is lowest byte and 0x633 is highest byte. It's recommended to clear initial Timer Tick value to 0.

### 2<sup>nd</sup>: Set Capture value of Timer0

Set registers TMR\_CAPTO\_0~TMR\_CAPTO\_3 (address 0x624~0x627). Address 0x624 is lowest byte and 0x627 is highest byte.

## 3rd: Set Timer0 as Mode 0 and enable Timer0

Set register TMR\_CTRL0 (address 0x620) [2:1] as 2b'00 to select Mode 0; Meanwhile set address 0x620[0] as 1b'1 to enable Timer0. Timer0 starts counting upward, and Tick value is increased by 1 on each positive edge of system clock until it reaches Timer0 Capture value.

### 5.1.3 Mode1 (GPIO Trigger Mode)

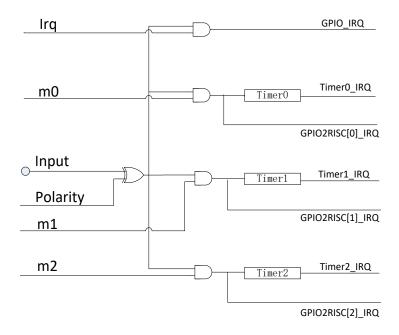

In Mode 1, GPIO is used as clock source. The "m0"/"m1"/"m2" register specifies the GPIO which generates counting signal for Timer0/Timer1/Timer2.

After Timer is enabled, Timer Tick (i.e. counting value) is increased by 1 on each positive/negative (configurable) edge of GPIO from preset initial Tick value. Generally the initial Tick value is set as 0. The "**Polarity**" register specifies the GPIO edge when Timer Tick counting increases.

Note: Refer to Section 7.1.2 for corresponding "m0", "m1", "m2" and "Polarity" register address.

Once current Timer Tick value matches the preset Timer Capture (i.e. timing value), timer stops counting and an interrupt is generated (if enabled).

Following is an example to show steps of setting Timer1 as Mode 1.

### 1<sup>st</sup>: Set initial Tick value of Timer1

Set initial Tick value of Timer1 via registers TMR\_TICK1\_0~TMR\_TICK1\_3 (address 0x634~0x637). Address 0x634 is lowest byte and 0x637 is highest byte. It's recommended to clear initial Timer Tick value to 0.

### 2<sup>nd</sup>: Set Capture value of Timer1

Set registers TMR\_CAPT1\_0~TMR\_CAPT1\_3 (address 0x628~0x62b). Address 0x628 is lowest byte and 0x62b is highest byte.

### 3<sup>rd</sup>: Select GPIO source and edge for Timer1

Select certain GPIO to be the clock source via setting "m1" register.

Select positive edge or negative edge of GPIO input to trigger Timer1 Tick increment via setting "Polarity" register.

### 4th: Set Timer1 as Mode 1 and enable Timer1

Set address 0x620[5:4] as 2b'01 to select Mode 1; Meanwhile set address 0x620[3] as 1b'1 to enable Timer1. Timer1 starts counting upward, and Timer1 Tick value is increased by 1 on each positive/negative (specified during the 3<sup>rd</sup> step) edge of the specified GPIO input until it reaches Timer1 Capture value.

### 5.1.4 Mode2 (GPIO Pulse Width Mode)

In Mode 2, system clock is used as the unit to measure the width of GPIO pulse. The "m0"/"m1"/"m2" register specifies the GPIO which generates control signal for Timer0/Timer1/Timer2.

After Timer is enabled, Timer Tick is triggered by a positive/negative (configurable) edge of GPIO pulse. Then Timer Tick (i.e. counting value) is increased by 1 on each positive edge of system clock from preset initial Tick value. Generally the initial Tick value is set as 0. The "Polarity" register specifies the GPIO edge when Timer Tick starts counting.

Note: Refer to Section 7.1.2 for corresponding "m0", "m1", "m2" and "Polarity" register address.

While a negative/positive edge of GPIO pulse is detected, timer stops counting and an interrupt is generated (if enabled). The GPIO pulse width could be calculated in terms of tick count and period of system clock.

Following is an example to show steps of setting Timer2 as Mode 2.

### 1<sup>st</sup>: Set initial Timer2 Tick value

Set Initial value of Tick via registers TMR\_TICK2\_0~TMR\_TICK2\_3 (address 0x638~0x63b). Address 0x638 is lowest byte and 0x63b is highest byte. It's recommended to clear initial Timer Tick value to 0.

### 2<sup>nd</sup>: Select GPIO source and edge for Timer2

Select certain GPIO source via setting "m2" register.

Select positive edge or negative edge of GPIO input to trigger Timer2 counting start via setting "Polarity" register.

### 3rd: Set Timer2 as Mode 2 and enable Timer2

Set address 0x620[7:6] to 2b'01 and address 0x621 [0] to 1b'1.

Timer2 Tick is triggered by a positive/negative (specified during the 2<sup>nd</sup> step) edge of the specified GPIO pulse. Timer2 starts counting upward and Timer2 Tick value is increased by 1 on each positive edge of system clock.

While a negative/positive edge of GPIO pulse is detected, Timer2 tick stops and an interrupt is generated (if enabled).

# 4th: Read current Timer2 Tick value to calculate GPIO pulse width

Read current Timer2 Tick value from address 0x638~0x63b.

Then GPIO pulse width is calculated as follows:

GPIO pulse width = System clock period \* (current Timer2 Tick – intial Timer2 Tick)

For initial Timer2 Tick value is set to the recommended value of 0, then:

GPIO pulse width = System clock period \* current Timer2 Tick.

### 5.1.5 Mode3 (Tick Mode)

In Mode 3, system clock is used as clock source.

After Timer is enabled, Timer Tick starts counting upward, and Timer Tick value is increased by 1 on each positive edge of system clock.

This mode could be used as time indicator. No interrupt will be generated. Timer Tick keeps rolling from 0 to 0xffffffff. When Timer tick overflows, it returns to 0 and starts counting upward again.

Following is an example to show steps of setting Timer0 as Mode 3.

### 1st: Set initial Tick value of Timer0

Set Initial value of Tick via address 0x630~0x633. Address 0x630 is lowest byte and address 0x633 is highest byte. It's recommended to clear initial Timer Tick value to 0.

### 2<sup>nd</sup>: Set Timer0 as Mode 3 and enable Timer0

Set address 0x620[2:1] as 2b'11 to select Mode 3, meanwhile set address 0x620[0] as 1b'1 to enable Timer0. Timer0 Tick starts to roll.

### 3rd: Read current Timer0 Tick value

Current Timer0 Tick value can be read from address 0x630~0x633.

### 5.1.6 Watchdog

Only Timer2 can be used as a watchdog timer, so that it could reset chip from unexpected hang up or malfunction.

Timer2 Tick has 32bits. Watchdog Capture has only 14bits, which consists of TMR\_CTRL2 (address 0x622) [6:0] as higher bits and TMR\_CTRL1 (address 0x621) [7:1] as lower bits. Chip will be reset when the Timer2 Tick[31:18] matches Watchdog Capture value.

The range of duration that can be set in watchdog is between T(sysclk)\*2^18 and T(sysclk)\*2^32, and T(sysclk) is the system clock period which is configurable. For example, if system clock is configured to 16MHz, then the upper time limit of watchdog reset is  $2^32/16$ MHz  $\approx 268$ s.

Following shows steps of setting Timer2 as watchdog timer.

### 1st: Clear Timer2 Tick value

Clear registers TMR\_TICK2\_0 ~TMR\_TICK2\_3 (address 0x638~0x63b). Address 0x638 is lowest byte and 0x63b is highest byte.

### 2<sup>nd</sup>: Enable Timer2

Set register TMR CTRLO (address 0x620) [6] as 1b'1 to enable Timer2.

### 3rd: Set 14-bit Watchdog Capture value and enable Watchdog

Set higher 7 bits and lower 7 bits of Watchdog Capture via address 0x622[6:0] and 0x621[7:1]. Meanwhile set address 0x622[7] as 1b'1 to enable Watchdog.

Then Timer2 Tick starts counting upwards from 0.

If bits[31:18] of Timer2 Tick value read from address 0x638~0x63b reaches Watchdog Capture, the chip will be reset, and the status bit in address 0x72[0] will be set as 1b'1 automatically. User can read the watchdog status bit after chip reset to check if the reset source is watchdog, and needs to write 1b'1 to this bit to manually clear the flag.

### 5.2 32kHz LTIMER

The ST17H56 also supports a low frequency (32kHz) timer "LTIMER" in suspend mode or deep sleep mode. This 32kHz timer can be used as one kind of wakeup source.

32kHz LTIMER related functions are all handled in the stack.

### 5.3 System Timer

The ST17H56 also supports a System Timer. Please refer to section **4.3.1** for System Timer clock.

In suspend mode, both System Timer and Timer0~Timer2 stop counting, and 32kHz Timer starts counting. When the chip restores to active mode, Timer0~Timer2 will continue counting from the number when they stops; In contrast, System Timer will continue counting from an adjusted number which is a sum of the number when it stops and an offset calculated from the counting value of 32kHz Timer during suspend mode.

System timer related functions are all handled in the stack.

| Manamania | D /\A/  | Function                      |

|-----------|---------|-------------------------------|

| Table 5   | 5- 2 Re | gister table for System Timer |

| Address | Mnemonic         | R/W | Function | Default Value |

|---------|------------------|-----|----------|---------------|

| 0x740   | Sys_timer[7:0]   | R/W |          | 0x00          |

| 0x741   | Sys_timer[15:8]  | R/W |          | 0x00          |

| 0x742   | Sys_timer[23:16] | R/W |          | 0x00          |

| Address | Mnemonic                     | R/W | Function                                                                                                                                                                                                                                                                                                                                        | Default Value |

|---------|------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 0x743   | Sys_timer[31:24]             | R/W | System timer counter, write to set initial value.                                                                                                                                                                                                                                                                                               | 0x00          |

| 0x748   | 32K_cal_latch[7:0]           | R   | 32k calibration count[7:0]                                                                                                                                                                                                                                                                                                                      | 0x00          |

| 0x749   | 32K_cal_latch[15:8]          | R   | 32k calibration count[15:8]                                                                                                                                                                                                                                                                                                                     | 0x00          |

| 0x74a   | Sys_timer_ctrl               | R/W | [7]: enable of system timer [6]: irq_mask for system timer 1: enable, 0: disable [5:4]: calibration mode 2'b00: 4 cycles of 32kHz clock 2'b01: 8 cycles of 32kHz clock 2'b10: 16 cycles of 32kHz clock (Default setting) 2'b11: 32 cycles of 32kHz clock [3]: calibration enable [2]: set to 0 [1]: rsvd [0]: set 32kHz timer 1: write; 0: read | 0x21          |

| 0x74b   | Sys_timer_cmd                | wo  | <ul><li>[7:6]: rsvd</li><li>[5]: clear 32k read latch update flag</li><li>[4]: rsvd</li><li>[3]: start 32k count write/read</li><li>[2:0]: rsvd</li></ul>                                                                                                                                                                                       | 0x00          |

| 0x74b   | Sys_timer_status             | RO  | [7]: rsvd [6]: rd_busy_man_2d [5]: rd_update_man_2d [4]: rsvd [3]: ss_sync [2]: cmd_set_tgl [1:0]: rsvd                                                                                                                                                                                                                                         | 0x00          |

| 0x74c   | sys_timer_32K_set [7:0]      | R/W | 32k timer write[7:0]                                                                                                                                                                                                                                                                                                                            | 0x00          |

| 0x74d   | sys_timer_32K_set [15:8]     | R/W | 32k timer write[15:8]                                                                                                                                                                                                                                                                                                                           | 0x00          |

| 0x74e   | sys_timer_32K_set [23:16]    | R/W | 32k timer write[23:16]                                                                                                                                                                                                                                                                                                                          | 0x00          |

| 0x74f   | sys_timer_32K_set<br>[31:24] | R/W | 32k timer write[31:24]                                                                                                                                                                                                                                                                                                                          | 0x00          |

| 0x750   | sys_timer_32K_read [7:0]     | R   | 32k timer read[7:0]                                                                                                                                                                                                                                                                                                                             | 0x00          |

| 0x751   | sys_timer_32K_read [15:8]    | R   | 32k timer read[15:8]                                                                                                                                                                                                                                                                                                                            | 0x00          |

| Address | Mnemonic                   | R/W | Function              | Default Value |

|---------|----------------------------|-----|-----------------------|---------------|

| 0x752   | sys_timer_32K_read [23:16] | R   | 32k timer read[23:16] | 0x00          |

| 0x753   | sys_timer_32K_read [31:24] | R   | 32k timer read[31:24] | 0x00          |

### \*Note:

32kHz clock calibration is related to 32k cycle numbers used. More cycles correspond to higher accuracy but more time. Generally 32kHz clock calibration will select 16 cycles of 32kHz clock.

The lower three bits of address 0x740 is invalid, therefore, the resolution should be 0.5us. The 0.5us resolution is only used for system timer read out. 32kHz clock calibration is done using every 16MHz clock cycle, so 32kHz clock accuracy is not affected.

### 1. Get 32kHz Timer count value

0x74a[0] = 0; //set to 32kHz Timer read mode

0x74a[3] = 1; //enable calibration to provide 16MHz clock count value related to 32kHz cycle (0x74a[5:4])

0x74a[7] = 1; //kick system timer to tick

0x74b[5] = 0; //clear 32kHz read update flag

Wait for 0x74b[5]==1; //wait for the next 32kHz update flag

Read 32kHz Timer value from 0x750

### 2. Set 32kHz Timer count value

0x74a[0] = 1; //set to 32kHz Timer write mode

Wait for 0x74b[6]==0; //see whether during 32kHz read

Write 32kHz Timer value to 0x74c;

0x74b[3] = 1; //start 32kHz write sync process